### Nanocrystal embedded MOS non volatile memory devices

Prof. C. K. Sarkar, Senior Member, IEEE IEEE EDS Distinguished Lecturer

Professor Dept. of Electronics & Telecommunication Engineering Jadavpur University Kolkata-700032, INDIA

> Phone/Fax: +91-33-24146217 E-mail: phyhod@yahoo.co.in http://www.jaduniv.edu.in http://www.ndslju.org

Introduction

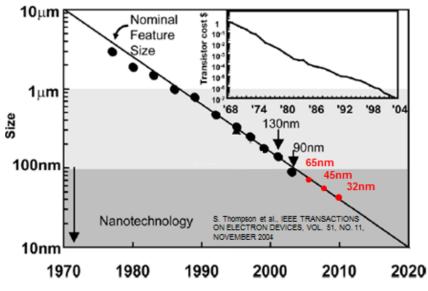

# Nanotechnology: A Revolutionary Concept

*"There's plenty of room at the bottom"* -Richard P. Feynman (Caltech, 29.12.1959)

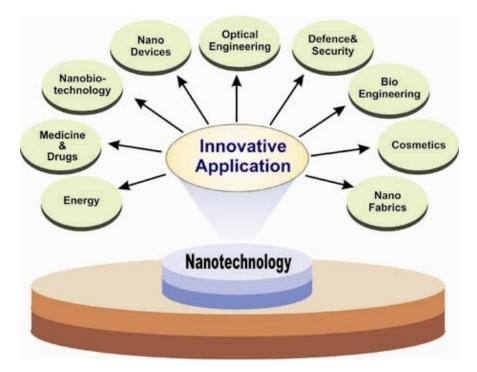

## Today Nanotechnology is a vast Inter-disciplinary Field

Source: http://lib.bioinfo.pl/blid:1739

The applications of Nanotechnology are numerous

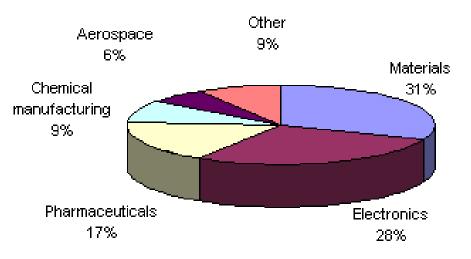

Source: NATIONAL SCIENCE FOUNDATION, USA

Nano-electronics holds a major share in this

# **MOS Memory Devices**

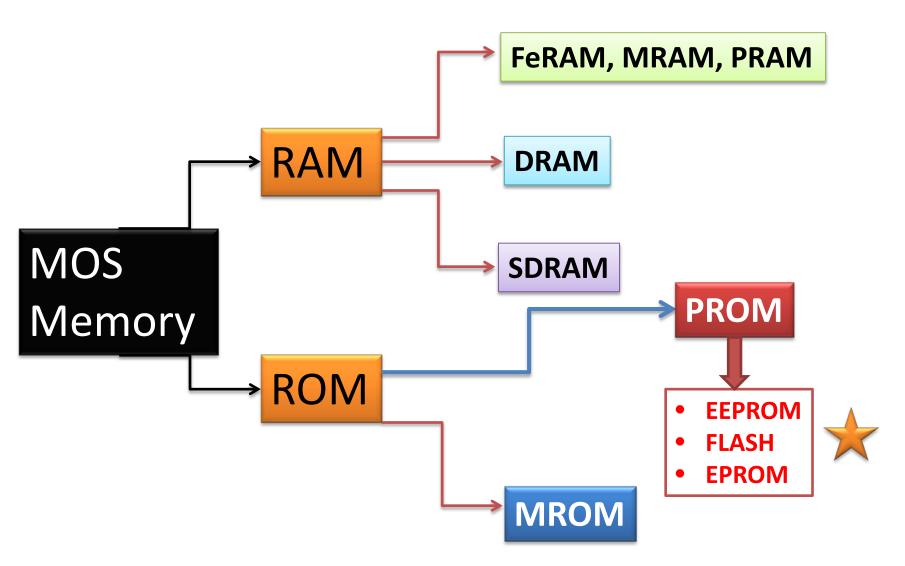

#### Various MOS Memory Devices

*Ref: A. Sengupta, C.K. Sarkar, The 4<sup>th</sup> IEEE International NanoElectronics Conf. (IEEE INEC ), June 21-24, 2011, Taiwan*

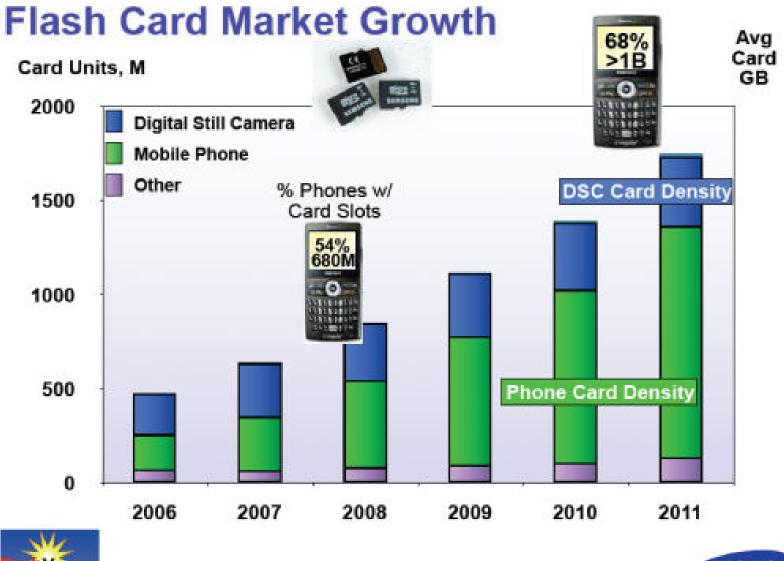

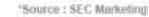

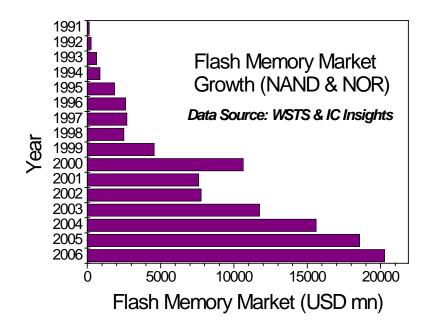

#### Flash Memory Market Share (Q3 2010)

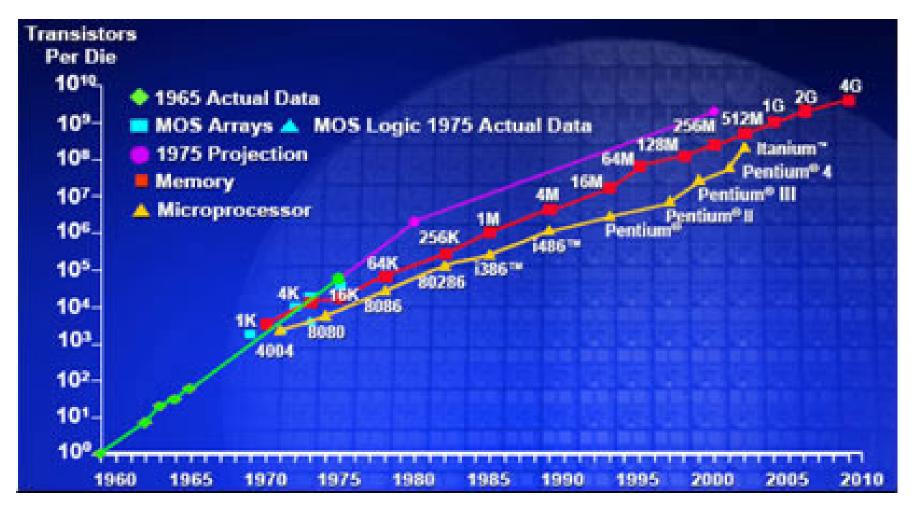

#### **Transistors per die of MOS Memory Devices**

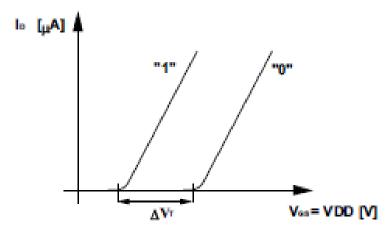

#### **MOSFET** memory and **MOS** capacitors

MOSFET memory devices rely on charge stored in the Floating Gate to cause a shift in the threshold/ flatband voltage.

Campardo et. al. VLSI Design of Non-Volatile Memories, Springer Verlag, Berlin Heidelberg 2005, pp. 50

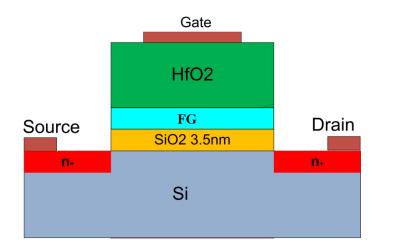

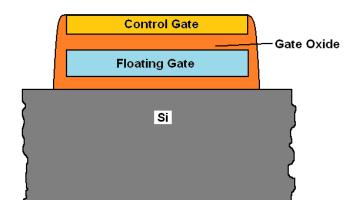

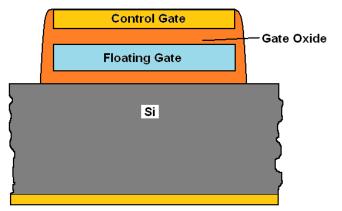

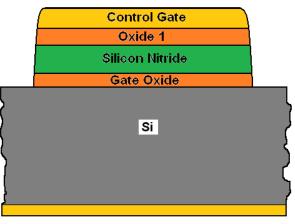

#### **Conventional MOS NVMs : Floating gate & SONOS**

Floating Gate MOS memory device

✓ Charges are stored in the Oxide-Nitride interface.

✓ Another variant MNOS useful for Aerospace/Military applications. ✓ Charges are stored in the polysilicon Floating Gate.

✓ Most commonly used for Flash memory applications.

SONOS MOS memory device

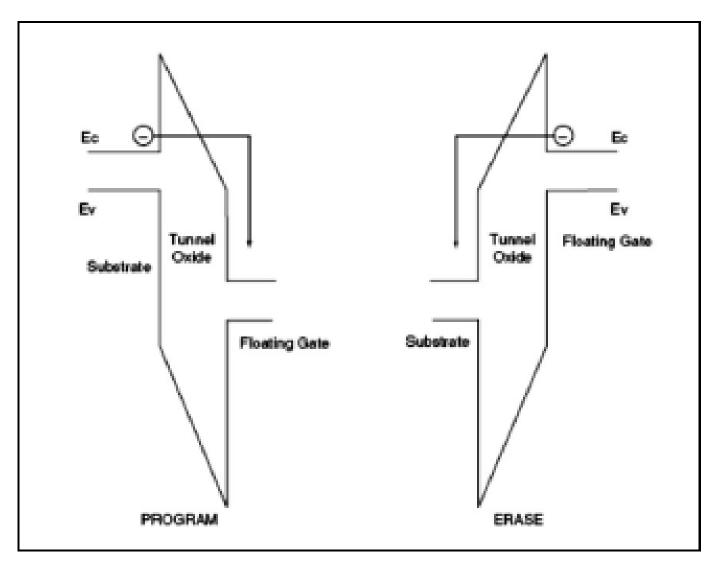

Fig. 2.3: Band diagrams of a Program /Erase operations of a floating gate cell {Ref: Micheloni et. al. Inside NAND Flash memories, Springer pp.91} **Disadvantage of conventional MOS Memory Devices**

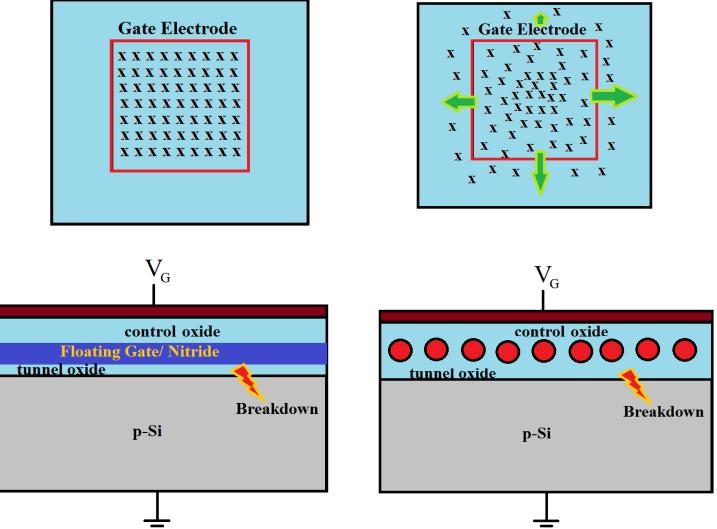

•With scaling and thinner tunnel oxides, leakage provides a major challenge. Also for portability lesser write voltages are required. Advantages of Nanotechnology may be applied to MOS devices. Nanocrystal embedded MOS NVMs can help in this regard.

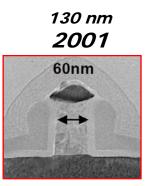

#### *Courtesy : Prof. Jakub Kedzierski IIT-Bombay/ MIT Lincoln Lab*

**Road-block:** Gate oxide tunneling current, the quantum nature of matter lets electrons penetrate the gate oxide

# Nanoparticles Based Floating Gate MOS Memory Structure

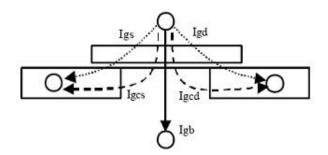

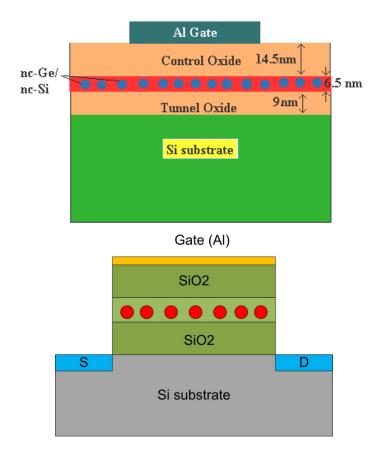

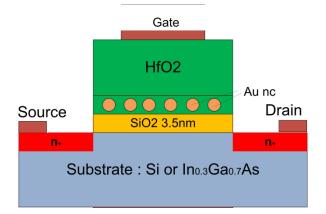

#### Nanoparticles embedded floating gate MOSFET and MOSCAP

Nanoparticles(nc) diameter in 5-6nm range.

>Confined in a narrow layer within  $SiO_2$  called embedded gate dielectric

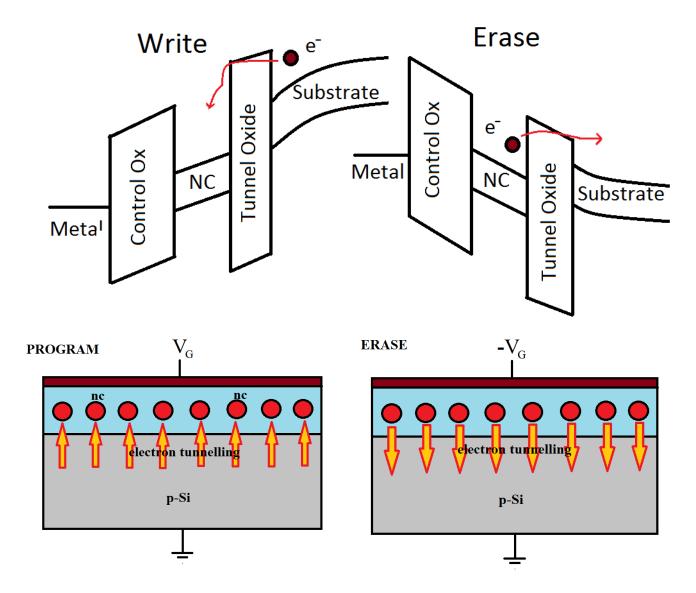

➢ Charging and discharging of nc carried out by electron tunneling

Electrons tunnel from Si substrate to gate electrode through gate dielectric

A thin tunneling barrier is formed at the interface of silicon substrate and composite gate dielectric

Comparison of nc-Si and nc-Ge embedded gate oxide MOS devices.

#### Write/Erase mechanism of such a device

# Advantages of Nanocrystal embedded <u>MOS NVM</u>

Recent

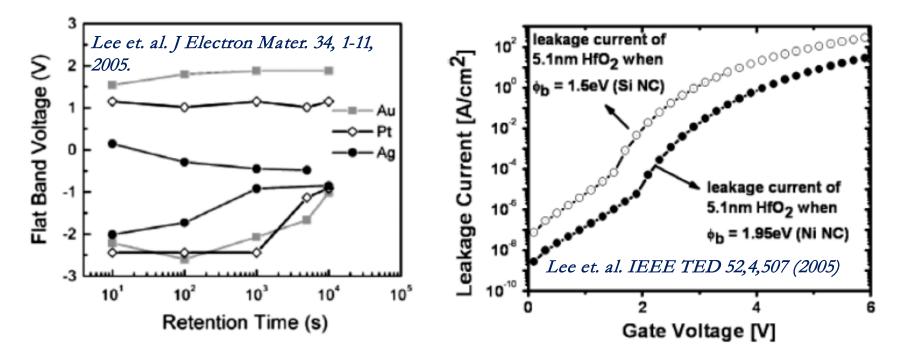

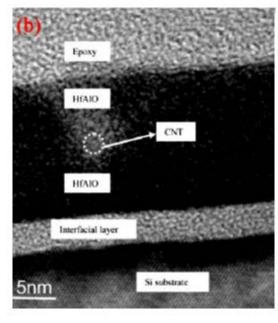

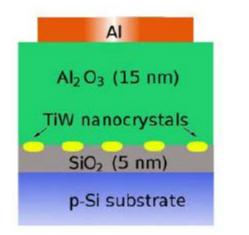

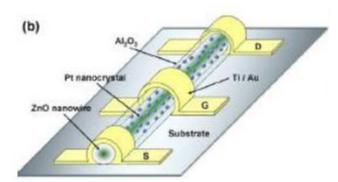

#### Metallic Nanocrystals

#### Use of Metallic nanocrystals like Ni, W, Ag, Au, Pt ncs.

Better charge storage, Lesser leakage, improved retention

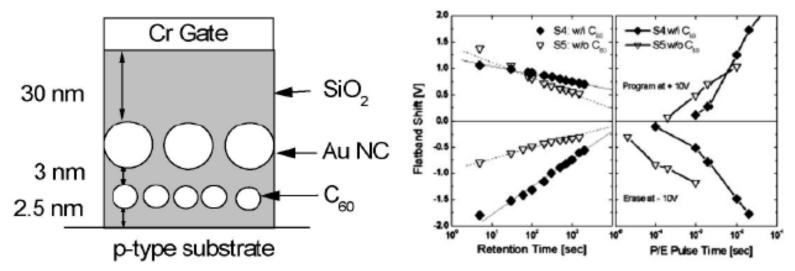

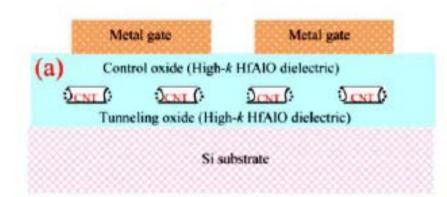

#### CNT/ C60 embedded MOS NVM

[T-H. Hou et. al. Device Research Conference, 2008, Issue Date: 23-25 June 2008 pp.275 - 276

[X. B. Lu and J. Y. Dai, Applied Physics Letters, vol. 88, no. 11, p. 113104, 2006.]

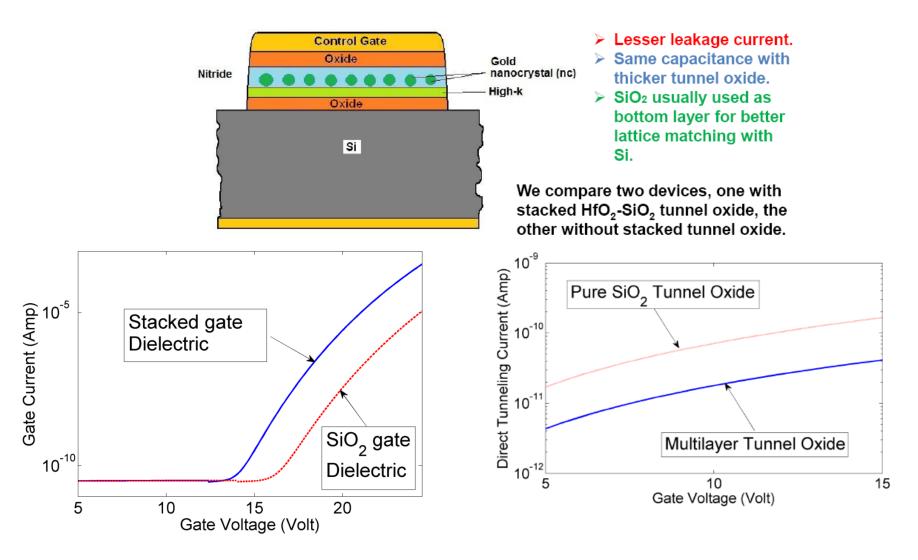

### Stacked High-k gate dielectrics

Yang et. al. Nanotechnology 21 (2010) 245201

Lo et. al. APPLIED PHYSICS LETTERS 94, 082901 2009]

- High-k materials help in suppressing the leakage.

- They have better charge retention then SiO<sub>2</sub> gate dielectrics.

- Better Program / Erase cycles

- endurance.

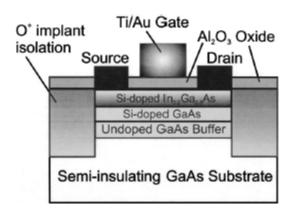

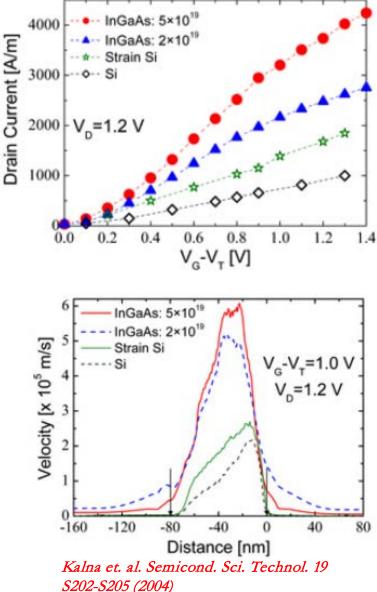

### **Compound semiconductor MOSFET**

- Compound semiconductors like In<sub>x</sub>Ga<sub>1-x</sub>As, GaN, InP, GaAs have better MOSFET performance than conventional Si or strained Si MOS.

- Such compound semiconductor MOS can be used for memory applications as well.

P. D. Ye et alApplied Physics Letters, vol. 84, no. 3, p. 434, 2004.

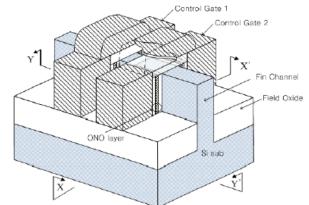

#### Multigate MOS NVM structures

Yeom et. al. Nanotechnology 19 (2008) 395204

*M.F. Hung, Applied Physics Letters, 98, 162108, 2011*

S. Oh, J. Kor. Phys. Soc., 55, 1, 263, 2009

MOS Non-Volatile Memories

# Why Modeling?

•Many device structures, many materials in terms of the embedded NCs and the substrate materials.

•Fabrication and testing is costly, time-consuming and requires infrastructure and manpower.

•A good model can thus act as a pointer in the right direction well before the actual fab is carried out.

## **Need for New Simulations**

- Standard device simulators like Sentaurus, Silvaco TCAD do not incorporate nanocrystal embedded MOS NVMs.

- Existing models are either involving a large amount of numerical solutions and rather complex iterative orthogonalization and extraction methods for 3D Kohn-Sham / Poisson-Schrodinger equations.

- No analytical models for advanced multi-gate nc embedded gate dielectric MOSFET NVMs.

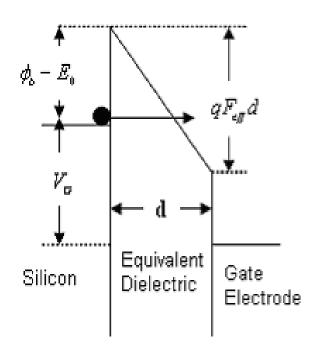

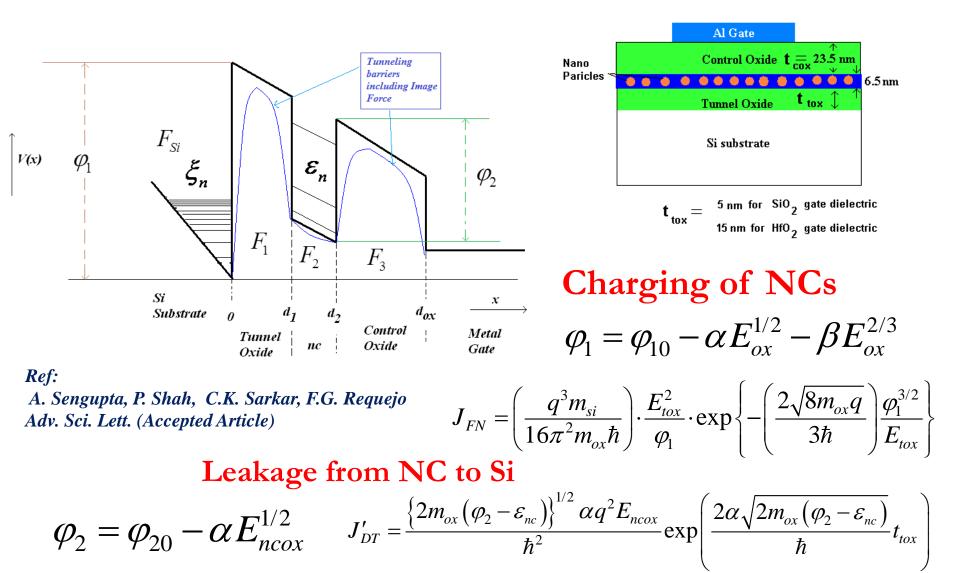

# Write Mechanism: Fowler – Nordheim Tunneling

> High Applied Gate voltage  $\rightarrow$  Fowler-Nordheim tunneling

>The barrier becomes Triangular in shape

Applied gate voltage

$$V > (\phi_{eff} - E_0)/q$$

Electrons tunnel from the conduction band of Si to conduction band of oxide through part of potential barrier

#### Band diagram of Fowler-Nordheim tunneling

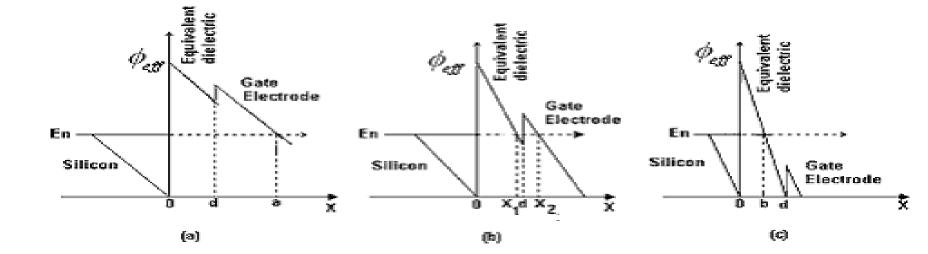

## Band Structure of Tunneling under Different Conditions of Applied Electric Field

Band bending at applied electric fields under different conditions (a)  $F_{eff}d < \phi_{eff} = E_n$ (b)  $\phi_{eff} = E_n < F_{eff}d < \phi - E_n$  (c)  $F_{eff}d > \phi - E_n$  **F-N Tunneling Probabilty Case I :**  $qF_{eff}d < (\phi_{eff} - E_o)$

$$D(E_{0}) = \exp\left(-\frac{4\sqrt{2m_{eff}}}{3q\hbar F_{eff}}\left[\left(\phi_{eff} - E_{0}\right)^{3/2} - \left(\phi_{eff} - E_{0} - qF_{eff}d\right)^{3/2}\right] - \frac{4\sqrt{2m}}{3q\hbar F}\left(\phi - E_{0} - qF_{eff}d\right)^{3/2}\right)$$

**Case II :**  $(\phi_{eff} - E_o) < qF_{eff}d < (\phi - E_o)$  $D(E_o) = \left\{ \sin^2 \theta_2 \cosh^2(\theta_3 - \theta_1) + \cos^2 \theta_2 \cosh^2[\theta_3 + \theta_1 + \ln(4)] \right\}^{-1}$

$$\hbar \theta_i = \int_{x_{i-1}}^{x_i} \left\{ 2m^* \left\| \left[ V(x) - E_0 \right] \right\| \right\}^{1/2} dx$$

**Case III :**

$$qF_{eff}d > (\phi - E_o)$$

$$D(E_0) = \exp\left(-\frac{4\sqrt{2m_{eff}}}{3q\hbar F_{eff}} \left(\phi_{eff} - E_0\right)^{3/2}\right)$$

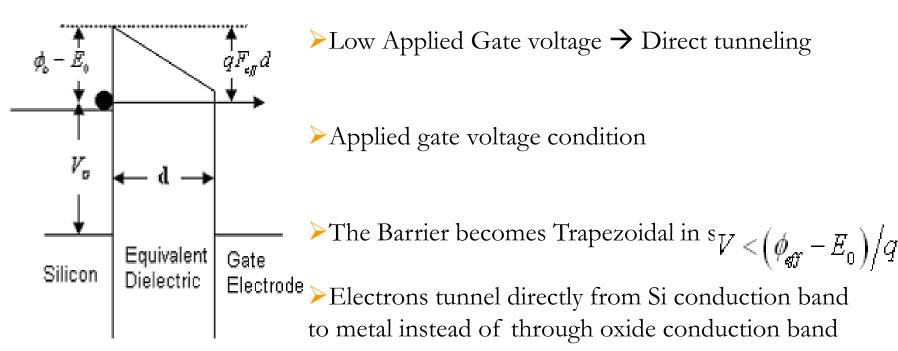

#### Leakage: Direct Tunneling

Band diagram for direct tunneling

$$J_{D} = \frac{\left\{2m_{eff}\left(\phi_{eff} - E_{0}\right)\right\}^{1/2} \alpha q^{2} V}{\hbar^{2} d} \exp\left(\frac{2\alpha \sqrt{2m_{eff}\left(\phi_{eff} - E_{0}\right)}}{\hbar}d\right)$$

# Parameters changed due to inclusion of Nanoparticles

Dielectric constant of SiO<sub>2</sub> embedded with nc-Si determined by using Maxwell-Garnett Effective Medium Approximation (EMA)

$$\epsilon_{nc-ox} = \frac{\epsilon_{ox} \left\{ 2\nu \left(\epsilon_{nc} - \epsilon_{ox}\right) + \left(\epsilon_{nc} + 2\epsilon_{ox}\right) \right\}}{\epsilon_{nc} + 2\epsilon_{ox} - \nu \left(\epsilon_{nc} - \epsilon_{ox}\right)} \qquad \epsilon_{eff} = \left\{ \frac{t_{ox}}{\epsilon_{ox} \cdot t} + \frac{t - t_{ox}}{\epsilon_{nc-ox} \cdot t} \right\}^{-1}$$

$$\geq \text{ Band gap energy has been modified}$$

$$E_{gnc} = E_{bulk} + \frac{\hbar^2 \pi^2}{2R^2} \left( \frac{1}{m_h^*} + \frac{1}{m_e^*} \right)$$

> Effective barrier height modified

$$\phi_{eff} = \frac{1}{2} \left[ \frac{E_{gsio2}}{2} + \frac{1}{2} \left( E_{gsio2} \cdot (1 - v) + v \cdot E_{gnc} \right) - E_{gsi} \right]$$

Electron effective mass has been changed

$$m_{eff} = \left[\frac{m_{sio2}d_{sio2}}{d} + \frac{m_{nc}(d - d_{sio2})}{d}\right]$$

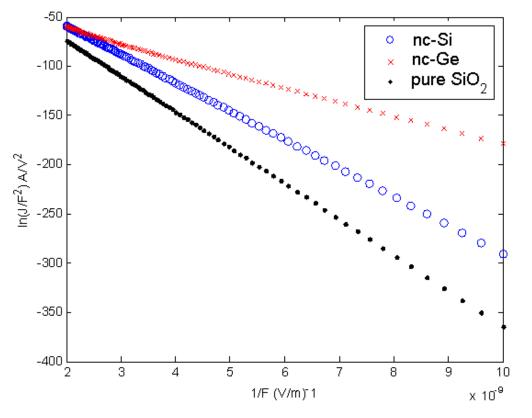

#### Simulated Fowler-Nordheim Plot

•FN plot compares the pure SiO<sub>2</sub> gate dielectric with the nc-Si and the nc-Ge embedded dielectric.

Both The nanoparticles embedded composite gate dieletrics show higher F-N tunneling current density than the pure SiO<sub>2</sub> dielectric.

The F-N tunneling current density is higher in nc-Ge embedded gate dielectric than the nc-Si embedded one.

#### Ref: G. Chakraborty, A. Sengupta, F.G. Requejo, C.K. Sarkar, J. Appl. Phys., 109, 064504 (2011).

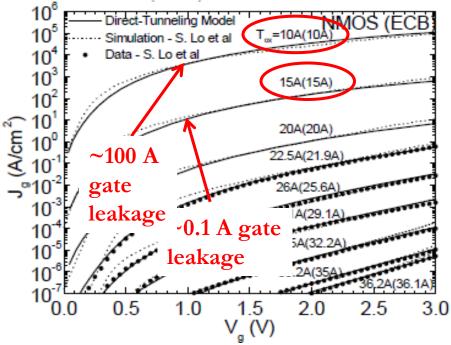

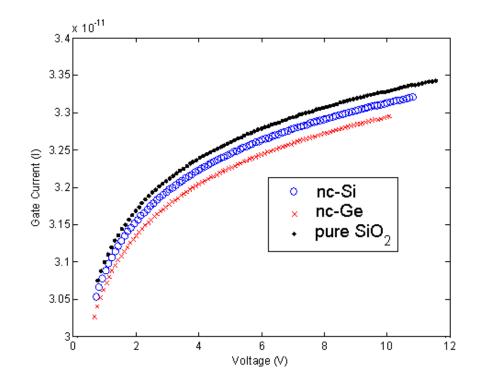

#### Simulated Leakage Current

•Here it is seen that the incorporation of nanocrystals in the gate oxide somewhat reduces the direct tunneling (leakage) current compared to pure  $SiO_2$  gate. Also it is evident that for the nc-Ge the value of the direct Tunneling current is the least.

*Ref: G. Chakraborty, A. Sengupta, F.G. Requejo, C.K. Sarkar, J. Appl. Phys., 109, 064504 (2011).*

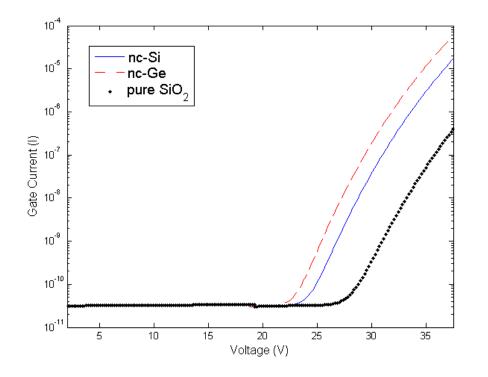

#### **Simulated I-V Characteristics**

Nanocrystalline particles

embedded gate oxide has an F N tunneling current few

decades greater compared to

pure SiO<sub>2</sub> gate.

Nanocrystal incorporation

markedly reduces the onset

voltage of F-N tunneling by

>5V-7V Volts.

The composite gate dielectric

The composite gate dielectric with nc-Ge has a slightly lower value of onset voltage for F-N tunneling compared to the nc-Si embedded one.

*Ref: G. Chakraborty, A. Sengupta, F.G. Requejo, C.K. Sarkar, J. Appl. Phys., 109, 064504 (2011).*

## **Modified Floating Gate Approach**

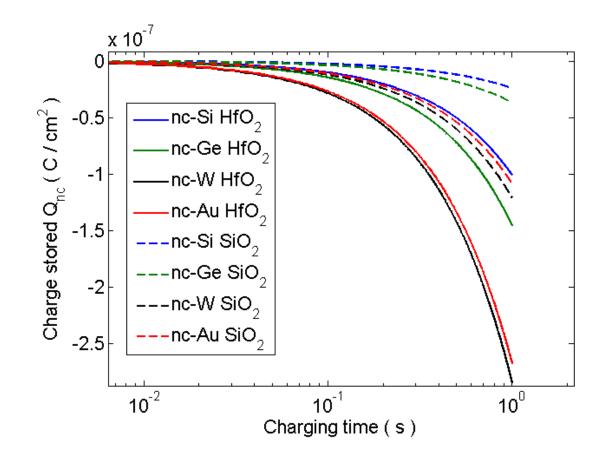

#### **Charge Storage of ncs**

•Metal Nanocrystals store higher amount of charge.

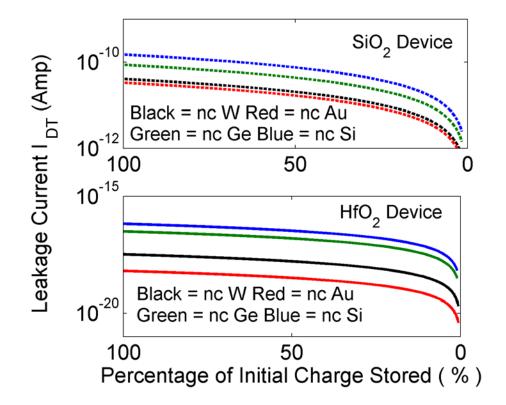

#### Simulated Leakage currents

•Metal Nanocrystals offer lesser leakage current compared to Semiconductor ncs.

• Use of High-k dielectrics can further reduce leakage current.

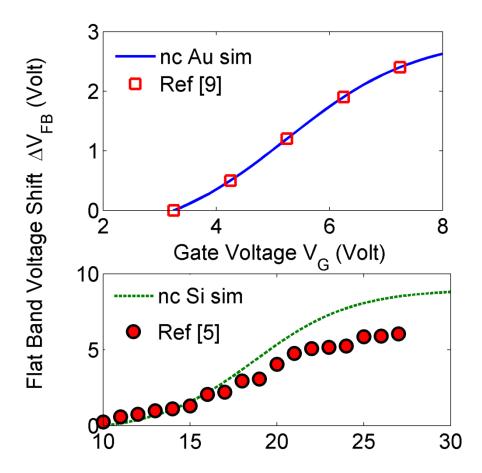

Flat-band Voltage Shift

•Flat-band shift simulations show a fair degree of agreement with experimental results.

## •nc embedded stacked gate devices show better performance than non-stacked structure.

*Ref: A. Sengupta, C.K. Sarkar, The 4<sup>th</sup> IEEE International NanoElectronics Conf. (IEEE INEC ), June 21-24, 2011, Taiwan*

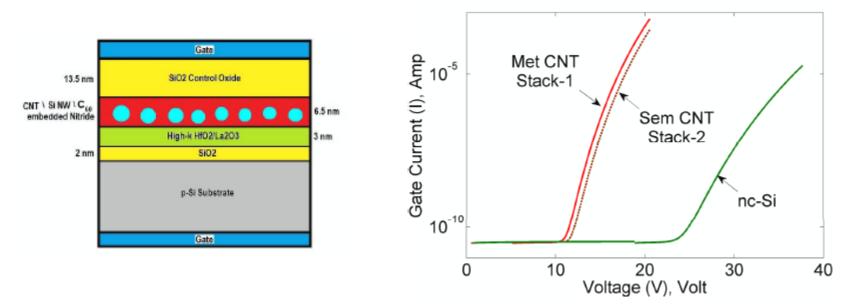

### Si Nanowire / CNT / Fullerene Embedded devices

•CNT / Si NW embedded devices show better performance than nc-Si embedded MOSCAP.

•HfO<sub>2</sub> is the better choice in combination with SiO<sub>2</sub> in stacked tunnel oxide.

*Ref: A. Sengupta, C.K. Sarkar, F.G. Requejo, J. Phys. D: Appl. Phys. Vol. 44, No. 36 pp. 405101 (2011).*

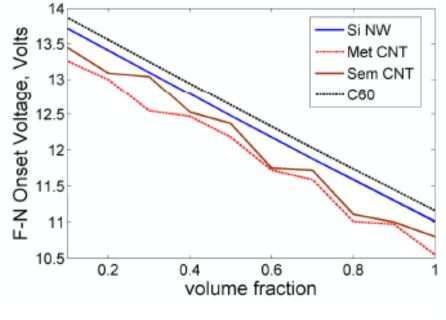

Study of Write Voltage variation with increasing volume fraction of the embedded nanomaterials.

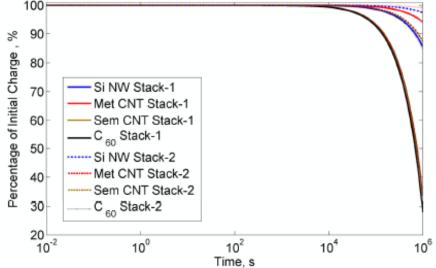

Study of charge decay during waiting time for the different structures.

*Ref: A. Sengupta, C.K. Sarkar, F.G. Requejo, J. Phys. D: Appl. Phys. Vol. 44, No. 36 pp. 405101 (2011).*

Fig 9: Decay of charge during the waiting time under a gate bias of -0.1 Volts.

| Parameter          |                            | Earlier                    |                            |                            |

|--------------------|----------------------------|----------------------------|----------------------------|----------------------------|

|                    |                            | Work{Ref [10]}             |                            |                            |

|                    | Met CNT Stack-1            | Si NW Stack-1              | C60 Stack-1                | nc-Si                      |

| F-N onset voltage  | 13.030 Volts               | 13.208 Volts               | 13.356 Volts               | 20.36 Volts                |

| F-N Tunnelling     | 6.205x10 <sup>-7</sup>     | 4.72 x10 <sup>-7</sup> A   | 3.2x10 <sup>-7</sup> A     | 1.05 x10 <sup>-10</sup> A  |

| Current (Amps) at  |                            |                            |                            |                            |

| 15 Volts           |                            |                            |                            |                            |

| Direct Tunnelling  | 3.179 x10 <sup>-11</sup> A | 3.184 x10 <sup>-11</sup> A | 3.237 x10 <sup>-11</sup> A | 3.320 x10 <sup>-11</sup> A |

| Current (Amps) (at |                            |                            |                            |                            |

| 7.5 Volts)         |                            |                            |                            |                            |

*Ref: A. Sengupta, C.K. Sarkar, F.G. Requejo, J. Phys. D: Appl. Phys. Vol.* 44, No. 36 pp. 405101 (2011).

| STACK-1 SIMULATION RESULTS |               |                         |                         |                      |                         |  |  |  |

|----------------------------|---------------|-------------------------|-------------------------|----------------------|-------------------------|--|--|--|

| Embedded nc                | Write ∀oltage | F-N Tunnelling          | Write Time (s) at       | Retention            | Erase Time (s) at       |  |  |  |

|                            | (Volt)        | Current (Amp)           | +14.5 Volts             | Time (s)             | 15V pulse height        |  |  |  |

|                            |               | at +15 Volts            |                         |                      |                         |  |  |  |

| Met CNT                    | 13.030        | 6.205×10 <sup>-7</sup>  | 0.150x10 <sup>-4</sup>  | 2.5x10 <sup>5</sup>  | 0.149 x10 <sup>-4</sup> |  |  |  |

| Sem CNT                    | 13.169        | 4.825x10 <sup>-7</sup>  | 0.193 x10 <sup>-4</sup> | 2.1x10*              | 0.176 x10 <sup>-4</sup> |  |  |  |

| Si NW                      | 13.209        | 4.72x10 <sup>-7</sup>   | 0.197 x10 <sup>-4</sup> | 6x10 <sup>4</sup>    | 0.188 x10 <sup>-4</sup> |  |  |  |

| C-60                       | 13.356        | 3.2 x10 <sup>-7</sup>   | 0.292 x10 <sup>-4</sup> | 1.94x10 <sup>4</sup> | 0.102 x10 <sup>-4</sup> |  |  |  |

| STACK-2 SIMULATION RESULTS |               |                         |                         |                      |                         |  |  |  |

| Embedded nc                | Write Voltage | F-N Tunnelling          | Write Time (s) at       | Retention            | Erase Time (s) at       |  |  |  |

|                            | (Volt)        | Current (Amp)           | +14.5 Volts             | Time (s)             | 15V pulse height        |  |  |  |

|                            |               | at +15 Volts            |                         |                      |                         |  |  |  |

| Met CNT                    | 13.702        | 2.275 x10 <sup>-7</sup> | 0.410 x10 <sup>-4</sup> | 1.15x10⁵             | 0.402 x10 <sup>-4</sup> |  |  |  |

| Sem CNT                    | 13.696        | 2.337 x10 <sup>-7</sup> | 0.399 x10 <sup>-4</sup> | 6.35x10⁴             | 0.303 x10 <sup>-4</sup> |  |  |  |

| Si NW                      | 13.850        | 1.607 x10 <sup>-7</sup> | 0.581 x10 <sup>-4</sup> | 6.5x10°              | 0.356 x10 <sup>-4</sup> |  |  |  |

| C-60                       | 13.991        | 1.352 x10 <sup>-7</sup> | 0.691 ×10 <sup>-4</sup> | 5.7x10 <sup>4</sup>  | 0.297 x10 <sup>-4</sup> |  |  |  |

#### NC embedded MOSFET NVMs

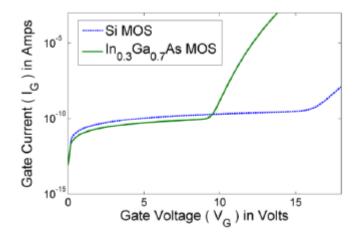

The compound semiconductor

(In<sub>0.3</sub>Ga<sub>0.7</sub>As) MOSFET

NVM shows lesser F-N

onset and lesser leakage.

Write voltages lowered by 3-4 Volts.

•We also study nc embedded MOSFET NVM devices.

Au nc was selected for better performance and based on reliability studies.

We compare Si and In<sub>0.3</sub>Ga<sub>0.7</sub>As substrates.

Ref: A. Sengupta, C.K. Sarkar, Int. J. Nanotechnol. (2011) {under review}.

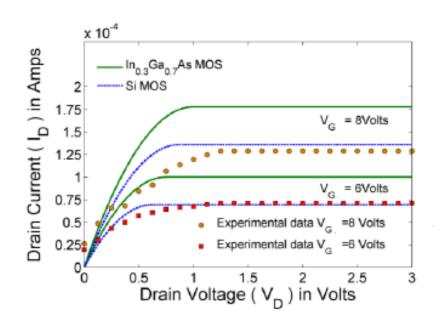

We also simulated the I<sub>D</sub>-V<sub>D</sub> (output) characteristics.

Compound semiconductor MOSFET shows higher drain currents.

•The simulated results for Si MOSFET NVM match experimental results of Mikhelashvili et. al. [Appl. Phys. Lett. 98, 212902 (2011) ]

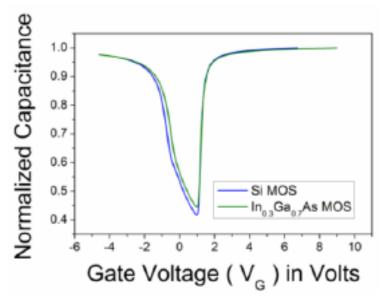

We also simulated the HFCV characteristics using the Berkeley Devices Simulator.

Compound semiconductor MOSFET shows slightly higher value of normalized capacitance.

Ref: A. Sengupta, C.K. Sarkar, Int. J. Nanotechnol. (2011) {under review}.

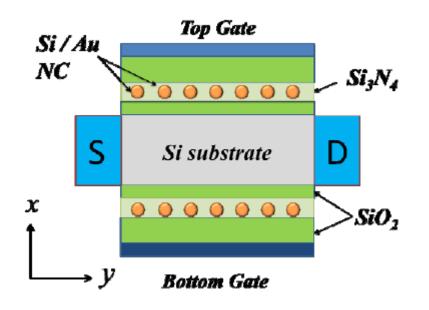

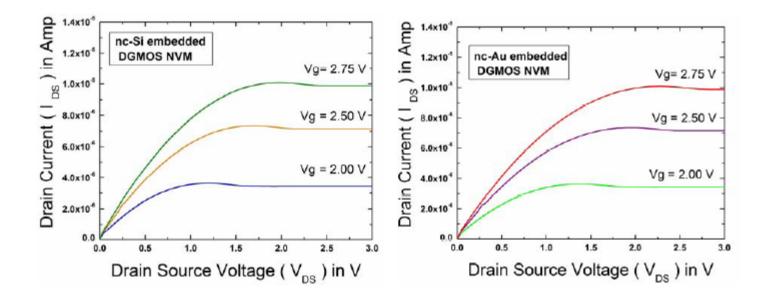

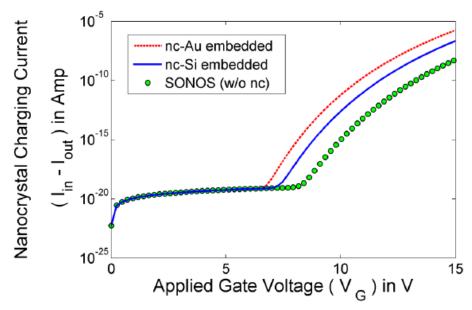

#### NC embedded DGMOSFET NVMs

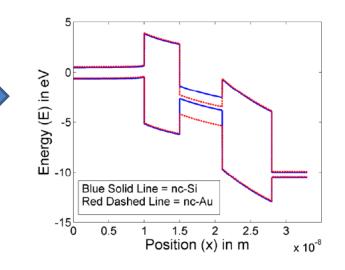

•The energy band diagram of a DGMOSFET NVM under a positive gate bias {simulation results}

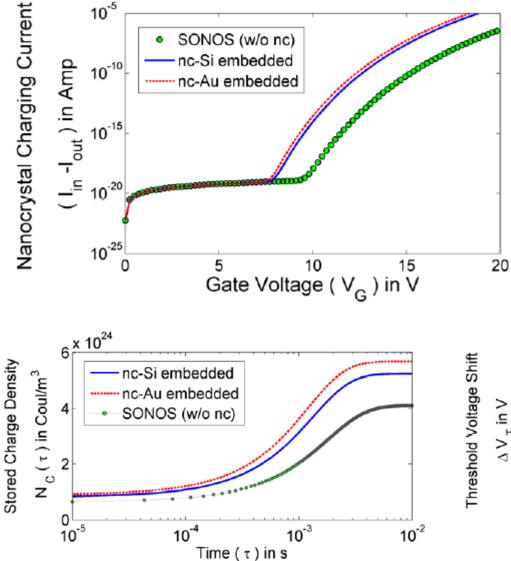

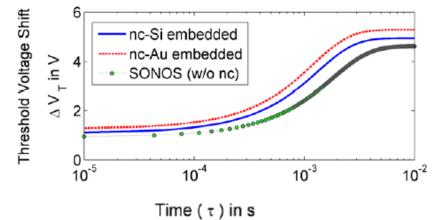

Ref: A. Sengupta, C.K. Sarkar, 'Surface Potential Based Analytical Modeling of Double Gate MOSFET with Si and Au Nano-dots Embedded Gate Dielectric for Non-Volatile Memory Applications' J. Appl. Phys. {Communicated}. DGMOSFETs offer better electrostatic control in the channel, than the planar MOS and therefore are becoming more and more popular.

Most DGMOSFET memories depend on SONOS architecture.

Nanocrystal embedded dielectric DGMOSFET NVM may be very useful.

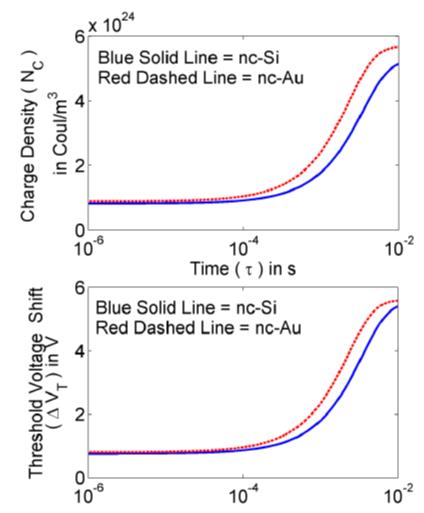

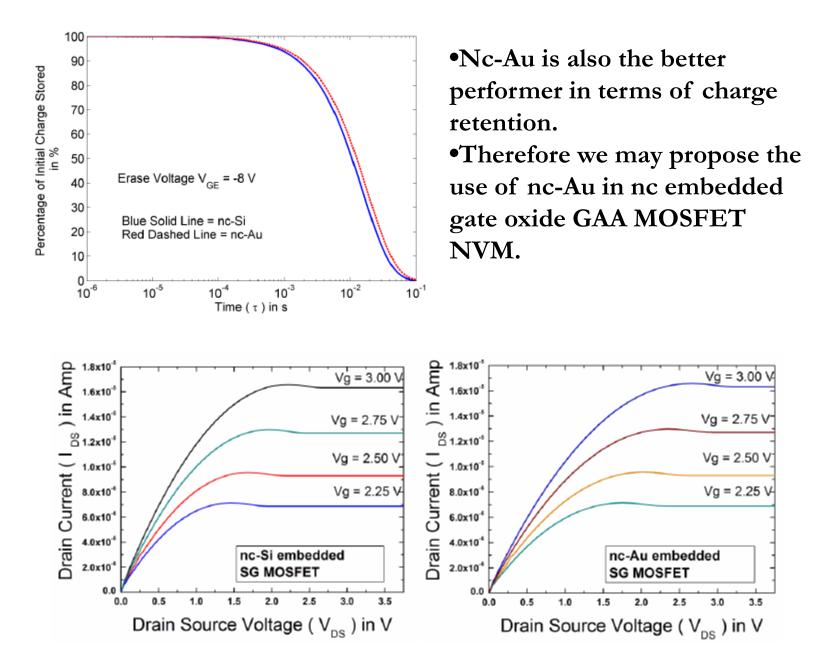

Nc embedded DGMOSFETs offer better write performance than their SONOS DGMOSFET counterparts, Au nc is the better among the two ncs compared.

Improvement of ~2V in terms of write voltage.

•Also more charge stored and higher Threshold Voltage (Vth) Shift.

•Almost similar magnitude of drain currents in the nc-Si and nc-Au embedded devices.

•Threshold Voltage of nc-Au embedded DGMOSFET, slightly higher.

•Slight tendency of  $V_{DS}$  de-clamping due to charging of nanocrsytals.

**Ref:** A. Sengupta, C.K. Sarkar, 'Surface Potential Based Analytical Modeling of Double Gate MOSFET with Si and Au Nano-dots Embedded Gate Dielectric for Non-Volatile Memory Applications' J. Appl. Phys. {Communicated}.

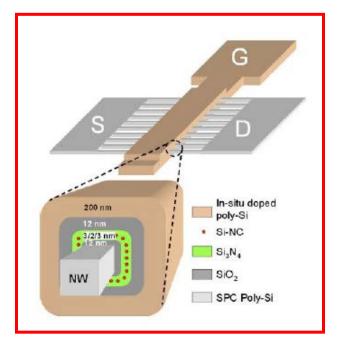

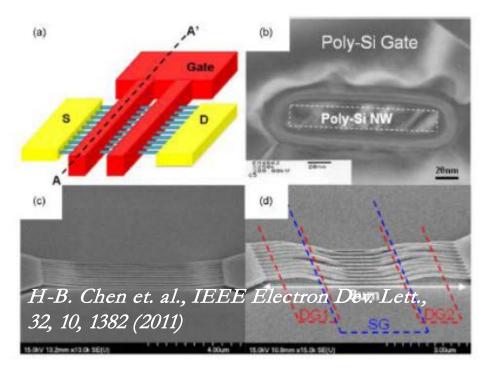

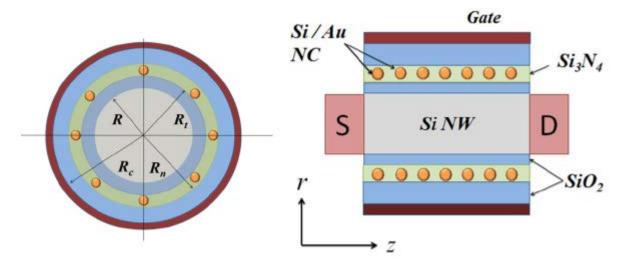

#### NC embedded GAA MOSFET NVMs

•We also study GAA (Gate All Around) MOS NVMs.

•These structures offer the best electrostatic control over the channel among all the advanced MOSFETs (i.e. better than DGMOS, Fin-FET,  $\Pi$ -Gate, or  $\Omega$ -gate MOSFETs).

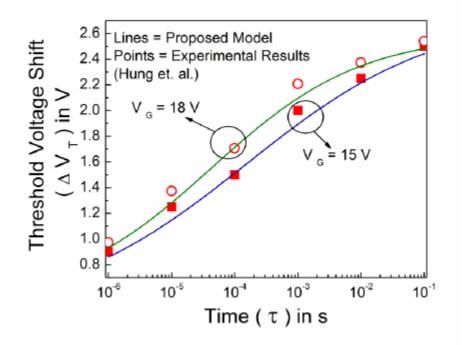

•GAA SONOS memories have been reported as well as recent experimental works on nc embedded gate dielectric GAA MOSFET memory. [Hung. Et. al. Appl. Phys. Lett.98,162108(2011) ]

*Ref: A. Sengupta, C.K. Sarkar*, 'Analytical Modelling of Si and Au Nanocrystal Embedded Multilayer Gate Dielectric Long Channel Silicon Nanowire Surround Gate MOSFET Non Volatile Memory Devices' *J. Phys. D: Appl. Phys. {Communicated}*.

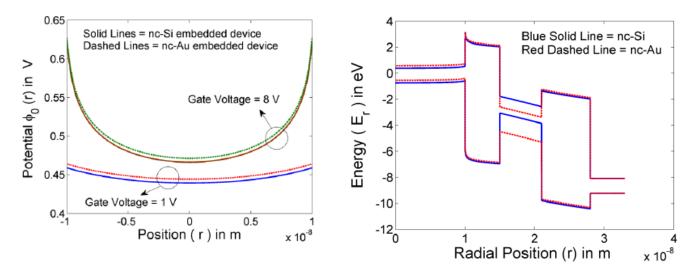

•We simulated the surface potentials, energy band diagrams, and the write voltages of Si and Au nc embedded gate dielectric GAA MOSFET NVMs.

Also more charge stored and higher Threshold Voltage (Vth)

Shift with nc-Au embedded GAA

MOSFET memory device.

The simulations tally well with experimental results by Hung et. al.

#### Conclusions

>MOS NVM devices are extensively used in flash memory based gadgets and computers.

> Floating Gate MOS memory elements mostly employed in flash memory devices.

Conventional Floating Gate MOS NVMs suffer from leakage, also write voltages need to be lowered.

➢Nanocrystals embedded Floating Gate MOS devices apply nanotechnology to improve device performance.

>Nc embedded MOS NVMs show lesser leakage current and lower write voltages compared to conventional MOS NVMs.

>Metal ncs and High-k dielectrics can improve the situation further.

≻Nc embedded MOS NVMs may be the memory device of choice in near future.

# Thank You

#### Visit our group's website

#### http://www.ndslju.org